# EE 330 Lecture 7

- Propagation Delay

- Stick Diagrams

- Technology Files

- Design Rules

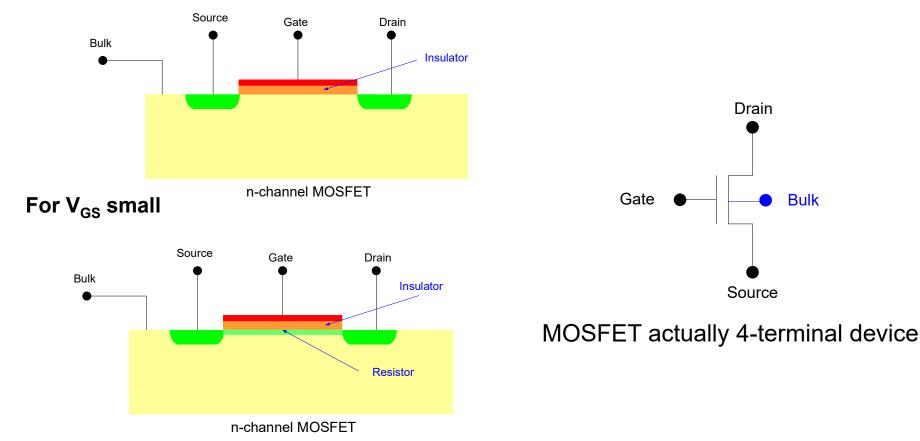

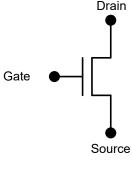

## Review from Last Time MOS Transistor Qualitative Discussion of n-channel Operation

#### For $V_{GS}$ large

- Region under gate termed the "channel"

- When "resistor" is electrically created, region where it resides in channel is termed an "inversion region"

## Review from Last Time MOS Transistor Qualitative Discussion of n-channel Operation

- For V<sub>GS</sub> large

- Electrically created inversion layer forms a "thin "film" resistor

- Capacitance from gate to <u>channel region</u> is distributed

- Lumped capacitance much easier to work with

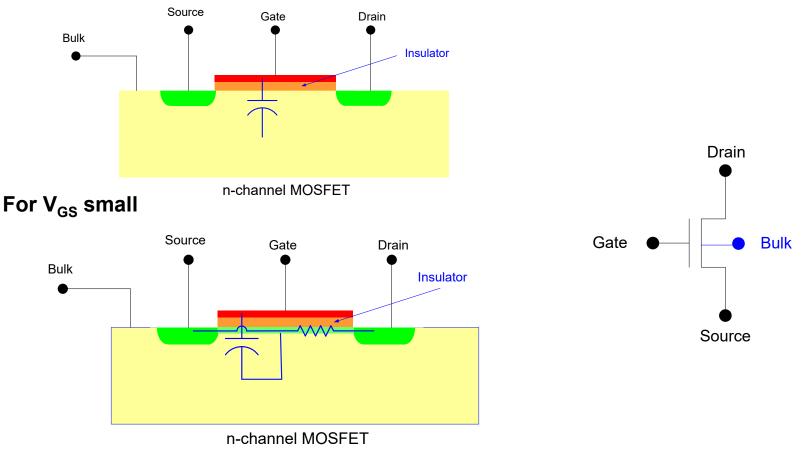

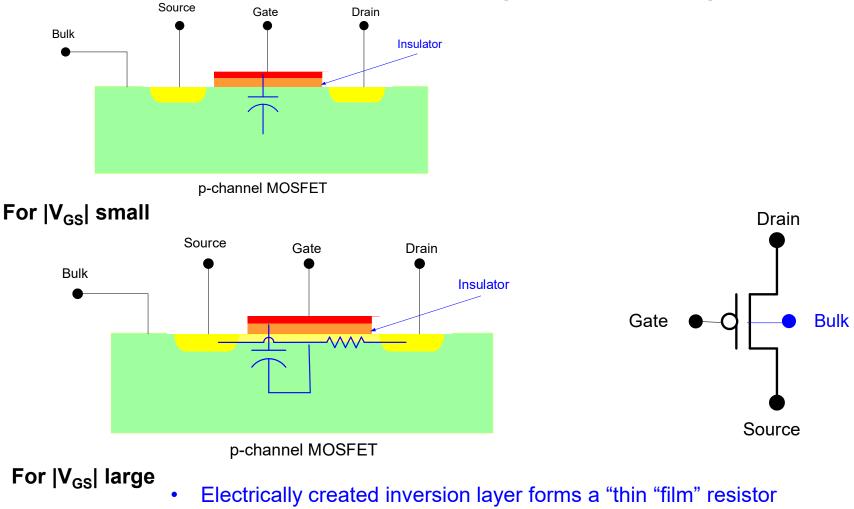

## Review from Last Time MOS Transistor

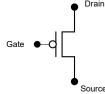

Qualitative Discussion of p-channel Operation

- Capacitance from gate to <u>channel region</u> is distributed

- Lumped capacitance much easier to work with

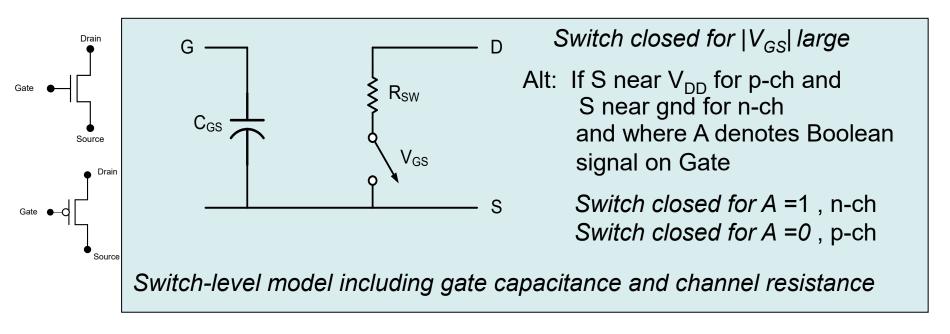

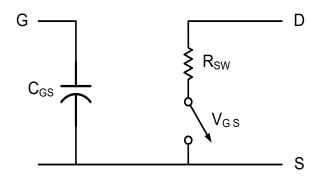

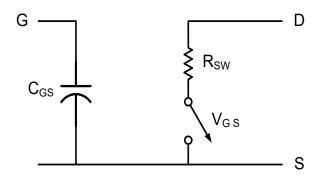

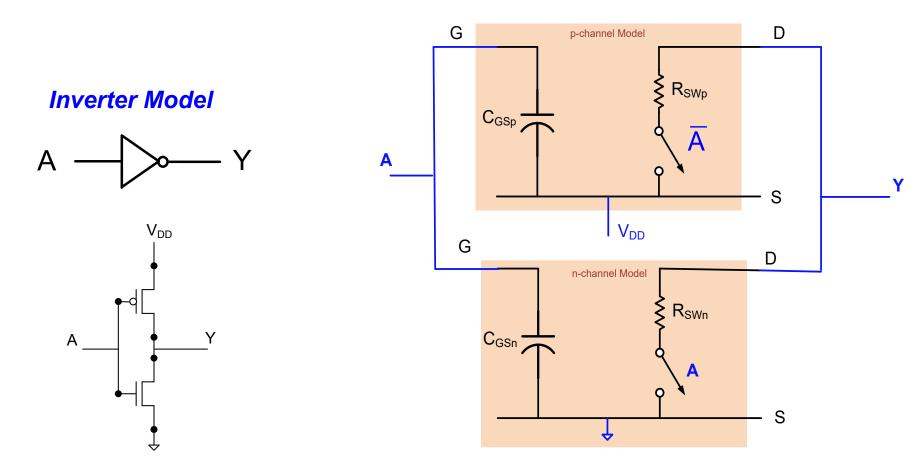

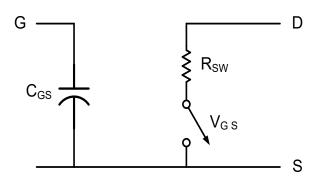

## Review from Last Time Improved Switch-Level Model

$C_{GS}$  and  $R_{SW}$  dependent upon device sizes and process For minimum-sized devices in a 0.5u process with  $V_{DD}=5V$  $C_{GS} \cong 1.5 \text{fF}$   $R_{sw} \cong \begin{array}{c} 2K\Omega & n-channel \\ 6K\Omega & p-channel \end{array}$

Considerable emphasis will be placed upon device sizing to manage  $C_{GS}$  and  $R_{SW}$

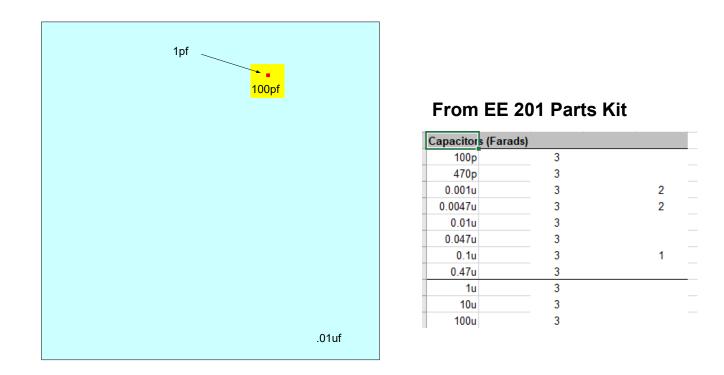

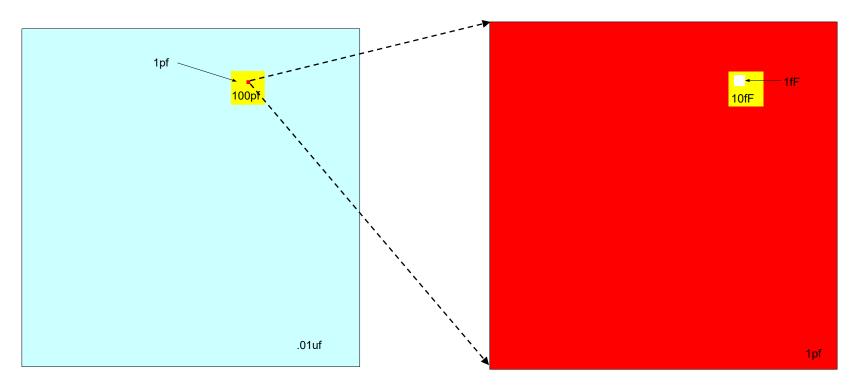

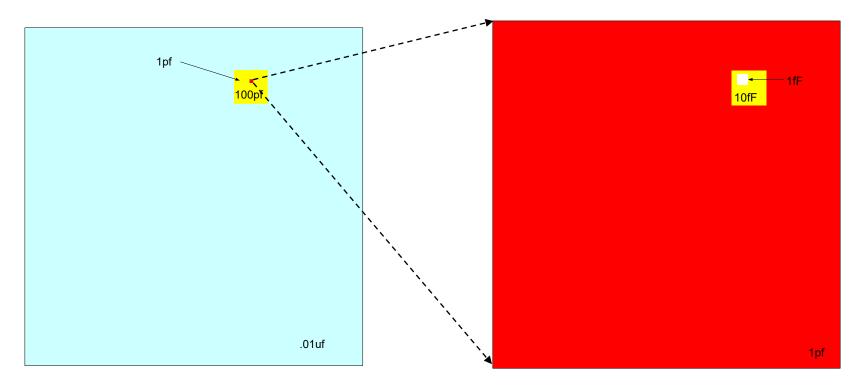

## Review from Last Time Is a capacitor of 1.5fF small enough to be neglected?

#### Area allocations shown to relative scale:

## Review from Last Time Is a capacitor of 1.5fF small enough to be neglected?

Area allocations shown to relative scale:

- Not enough information at this point to determine whether this very small capacitance can be neglected

- Will answer this important question later

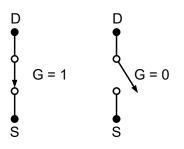

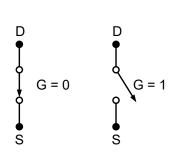

2. Improved switch-level model

Switch closed for  $V_{GS}$ = large Switch open for  $V_{GS}$ = small

#### Other models will be developed later

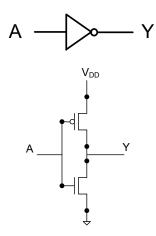

## **Review from Last Time** Model Summary (for p-channel)

#### 2. Improved switch-level model

Switch closed for  $|V_{GS}|$  = large Switch open for  $|V_{GS}|$  = small

#### Other models will be developed later

# **Propagation Delay**

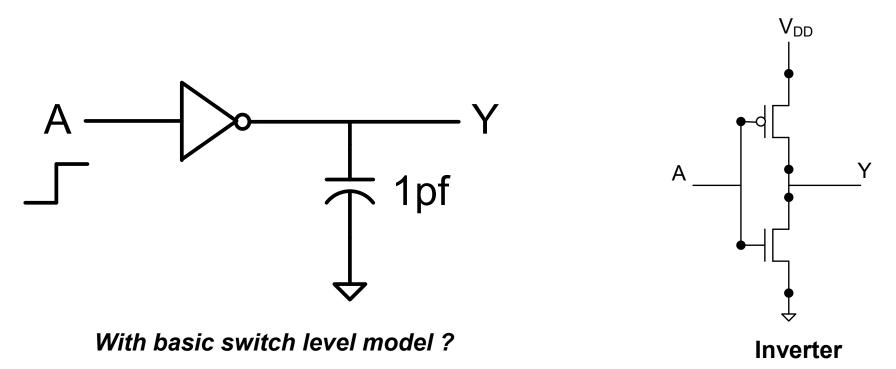

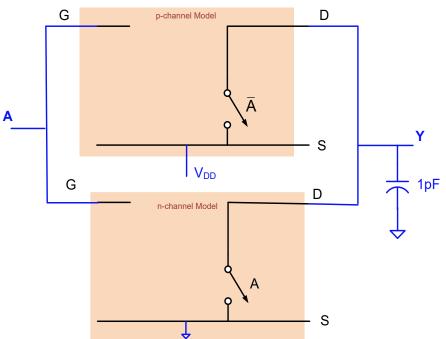

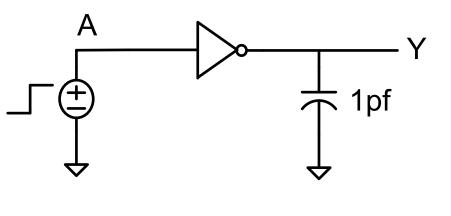

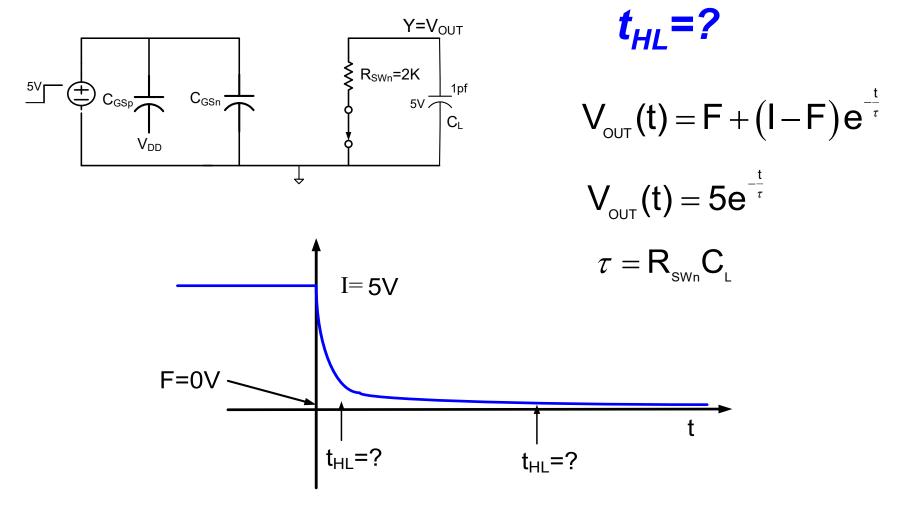

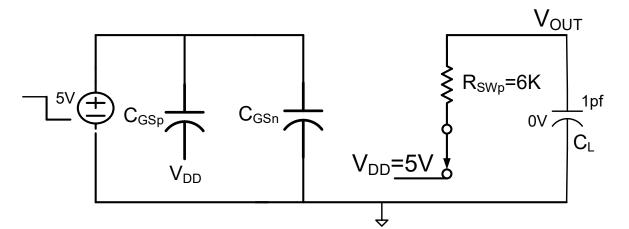

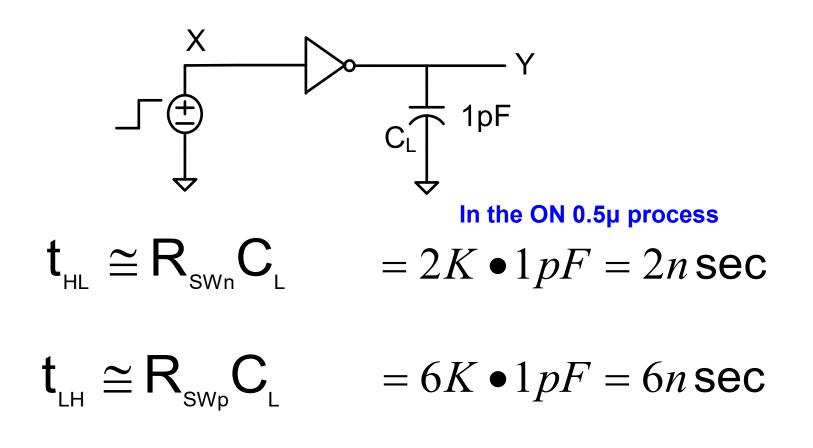

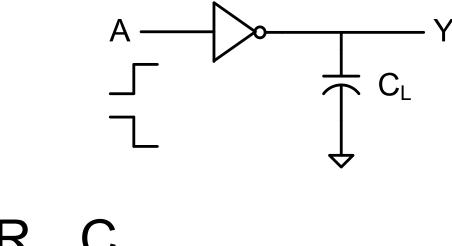

# Example What are t<sub>HL</sub> and t<sub>LH</sub>?

Assume V<sub>DD</sub>=5V

With improved switch level model ?

# Example

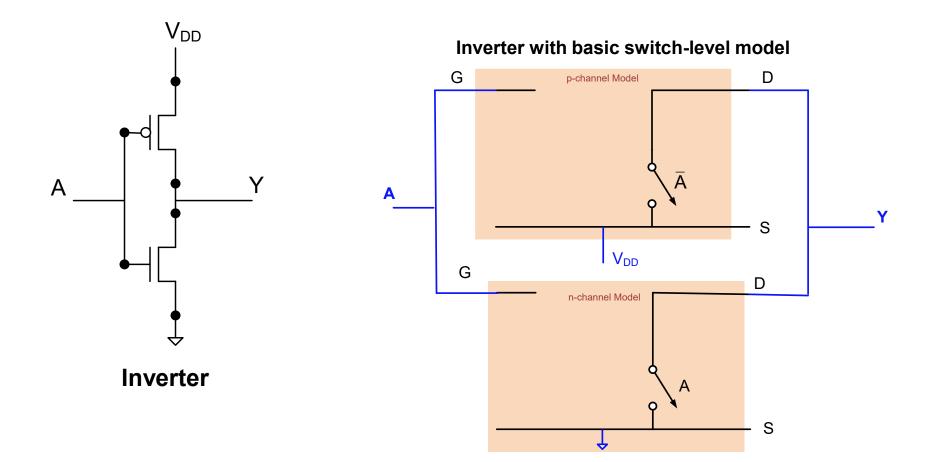

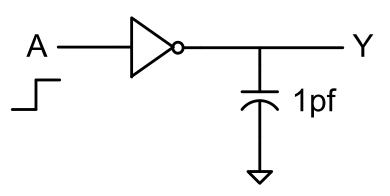

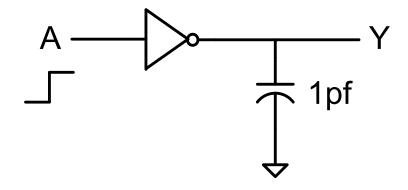

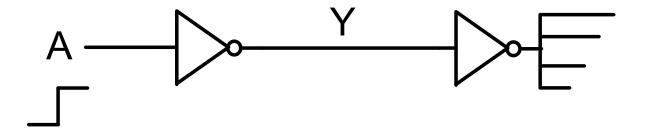

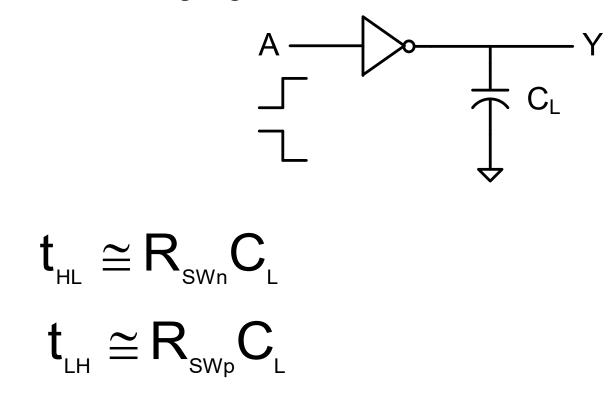

## Example What are t<sub>HL</sub> and t<sub>LH</sub> at output?

Assume ideal step at A input

With basic switch level model

t<sub>HL</sub>=t<sub>LH</sub>=0

*With simple switch-level model* t<sub>HL</sub>=t<sub>LH</sub>=0

With improved model ?

Α

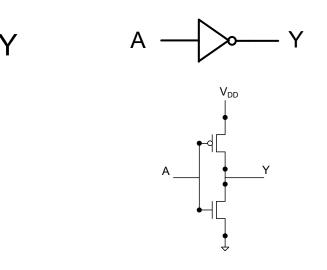

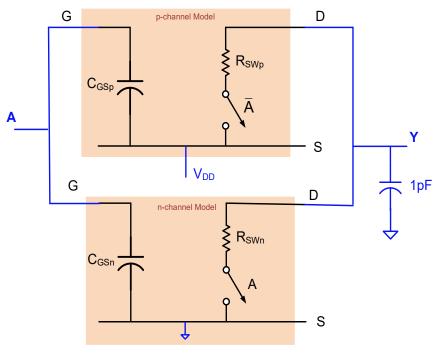

**Inverter Model?**

1pf

#### Inverter with improved model

#### **Inverter with Improved Model**

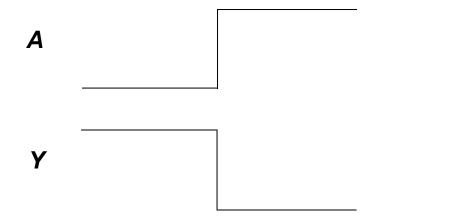

With improved model t<sub>HL</sub>=?

To initiate a HL output transisition, assume Y has been in the high state for a long time and lower switch closes at time t=0

5V is the initial condition on  $C_L$

Recall: Step response of any first-order network with LHP pole can be written as

$$\mathbf{y}(\mathbf{t}) = \mathbf{F} + (\mathbf{I} - \mathbf{F}) \mathbf{e}^{-\frac{1}{\tau}}$$

where F is the final value, I is the initial value and T is the time constant of the circuit

(from Chapter 7 of Nilsson and Riedel)

For the circuit above, F=0, I=5 and  $\tau = R_{swn}C_{L}$

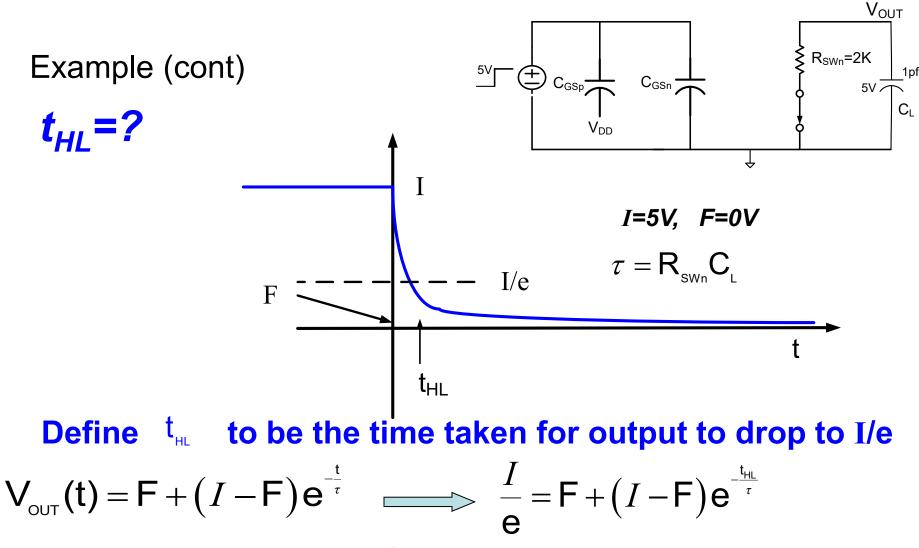

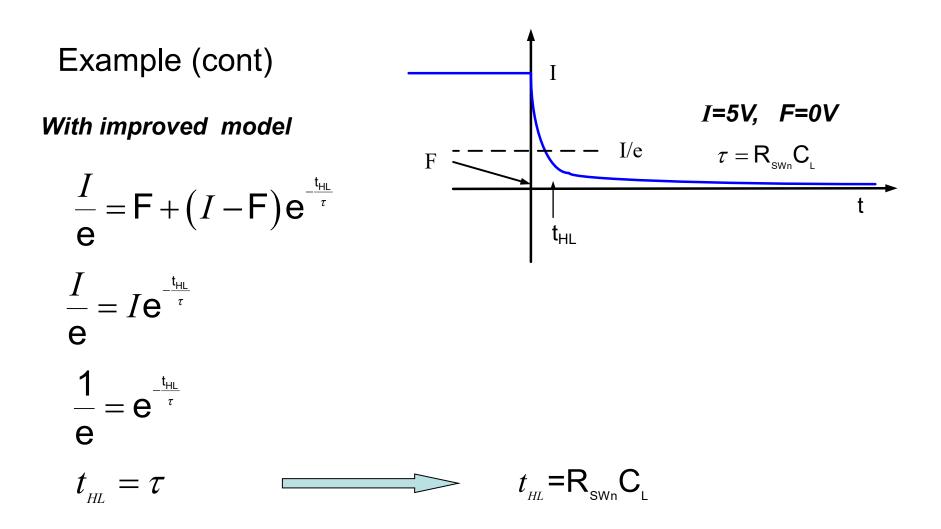

#### With improved model

how is t<sub>HL</sub> defined?

Is this simply a mathematical definition or does it have some practical significance?

$t_{HL}$  as defined here and as verified by experimental verification has proven useful at analytically predicting response time of circuits

Both experimental results and accurate computer simulations show that this reasonably accurately predicts how quickly following stages recognize that a logic transition has taken place !!

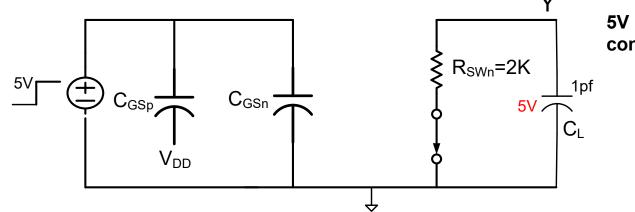

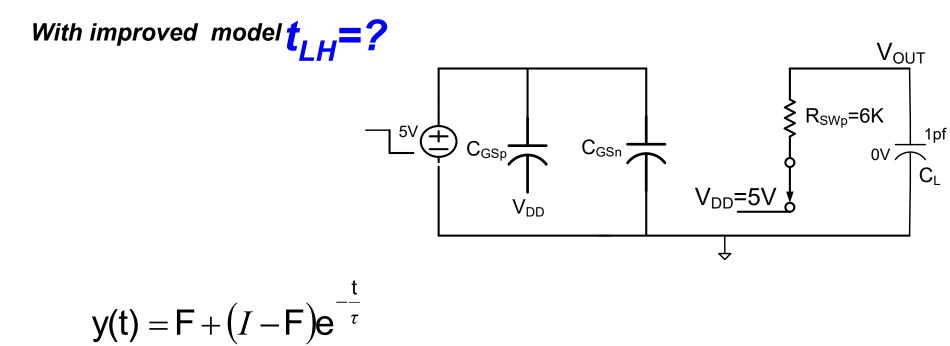

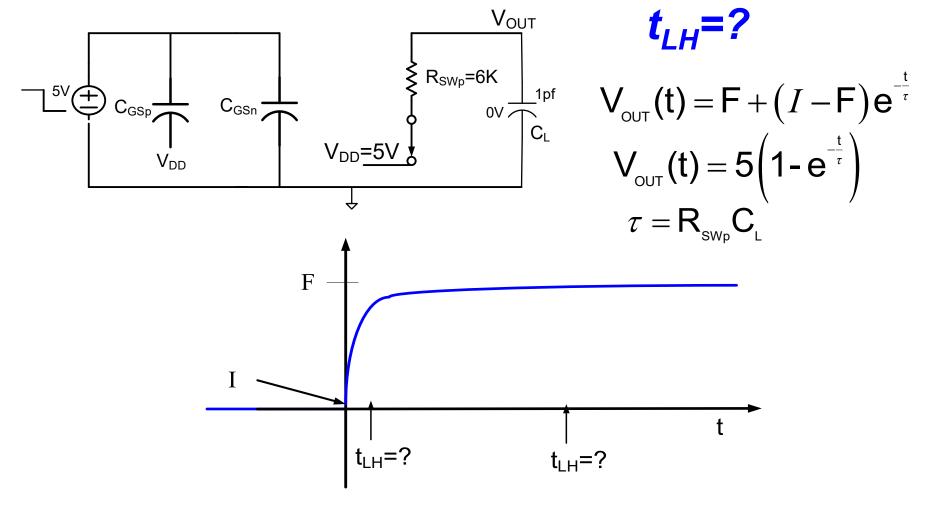

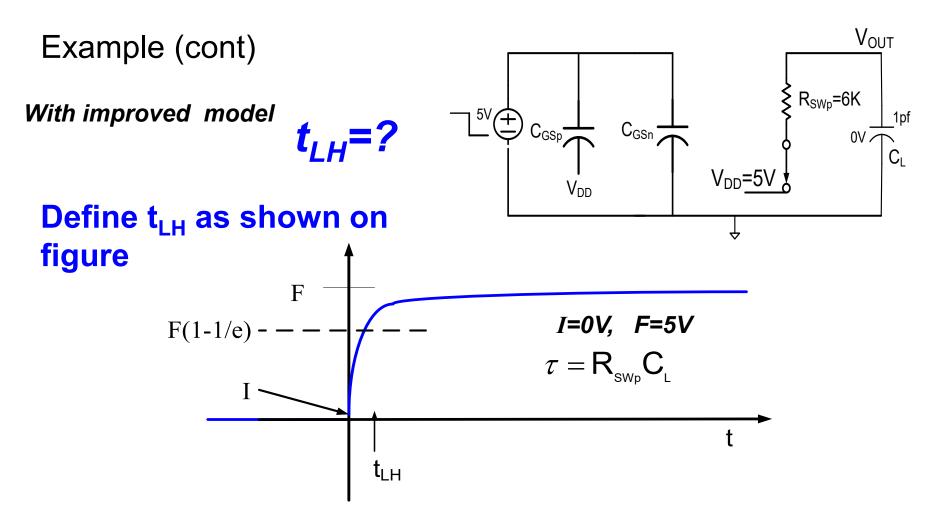

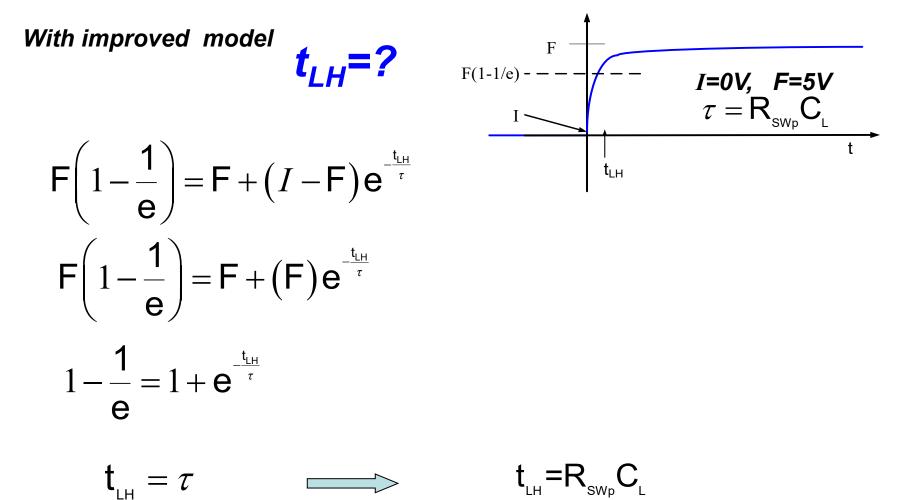

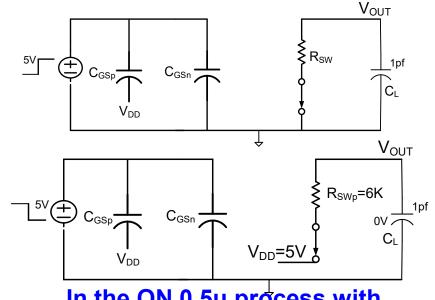

#### With improved model **t**<sub>LH</sub>=?

Assume output in low state for a long time and upper switch closes at time t=0

G

p-channel Model

R<sub>SWp</sub>

Ā

$R_{SWn}$

Α

0V is the initial condition on  $C_L$

D

S

D

S

Υ

1pF

Α

For this circuit (specifically on the right), F=5, I=0 and  $\tau = R_{sub}C_{I}$

With improved model

how is  $t_{LH}$  defined?

*t<sub>LH</sub>* as defined has proven useful for analytically predicting response time of circuits

$$V_{out}(t) = F + (I - F)e^{-\frac{t}{\tau}} \qquad \Longrightarrow \qquad F\left(1 - \frac{1}{e}\right) = F + (I - F)e^{-\frac{t_{LH}}{\tau}}$$

With improved model

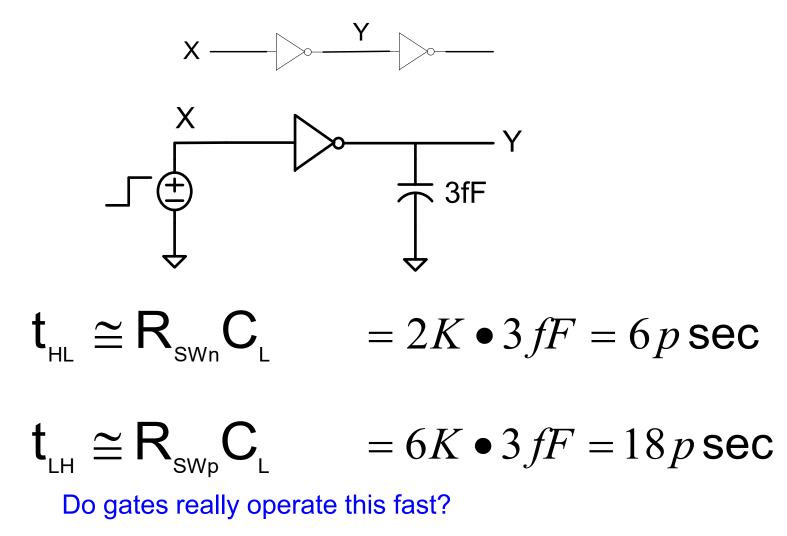

In the ON 0.5u process with minimum-sized devices

$$\mathbf{t}_{_{\mathrm{HL}}} \cong \mathbf{R}_{_{\mathrm{SWn}}} \mathbf{C}_{_{\mathrm{L}}} = 2K \cdot 1pF = 2n \operatorname{sec}$$

$\mathbf{t}_{_{\mathrm{LH}}} \cong \mathbf{R}_{_{\mathrm{SWp}}} \mathbf{C}_{_{\mathrm{L}}} = 6K \cdot 1pF = 6n \operatorname{sec}$

Note this circuit is quite fast !

Note that t<sub>HL</sub> is much shorter than t<sub>LH</sub>

Often C<sub>L</sub> will be even smaller and the circuit will be much faster !!

Summary: What is the delay of a minimum-sized inverter driving a 1pF load?

# Improved switch-level model

Switch closed for V<sub>GS</sub>= large

Switch open for  $V_{GS}$  = small

- Previous example showed why R<sub>sw</sub> in the model was important

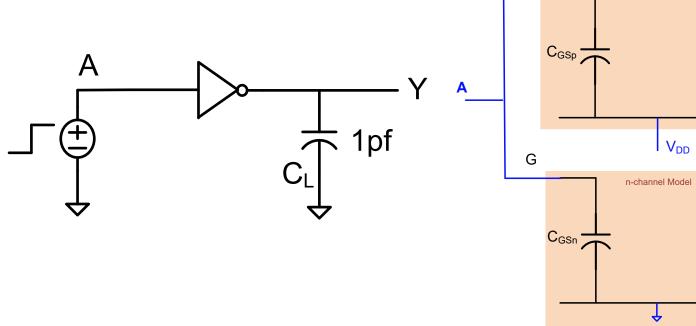

- But of what use is the C<sub>GS</sub> which did not enter the previous calculations?

For minimum-sized devices in a 0.5µ process

$$\mathbf{C}_{GS} \cong \mathbf{1.5fF} \qquad \mathbf{R}_{sw} \cong \begin{array}{c} \mathbf{2K\Omega} & \mathbf{n} - \mathbf{channel} \\ \mathbf{6K\Omega} & \mathbf{p} - \mathbf{channel} \end{array}$$

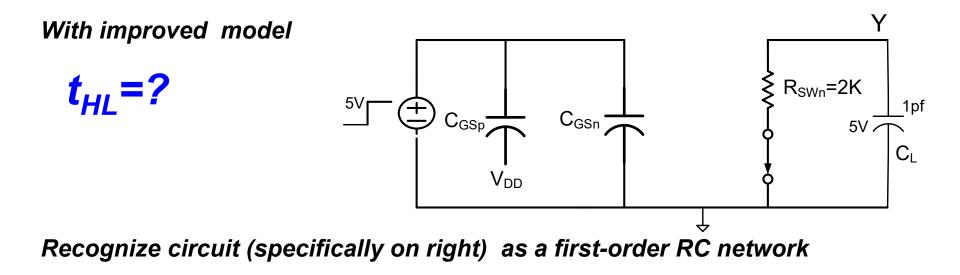

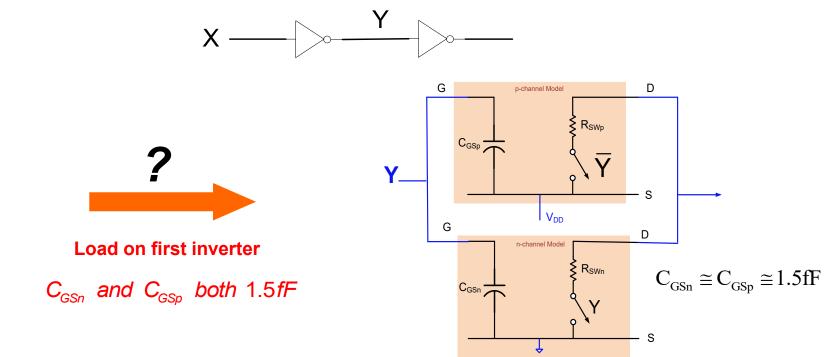

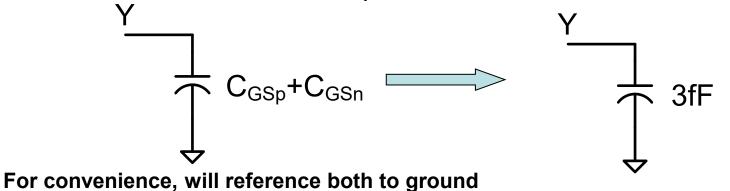

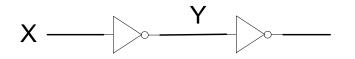

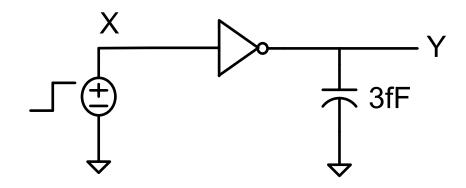

One gate often drives one or more other gates !

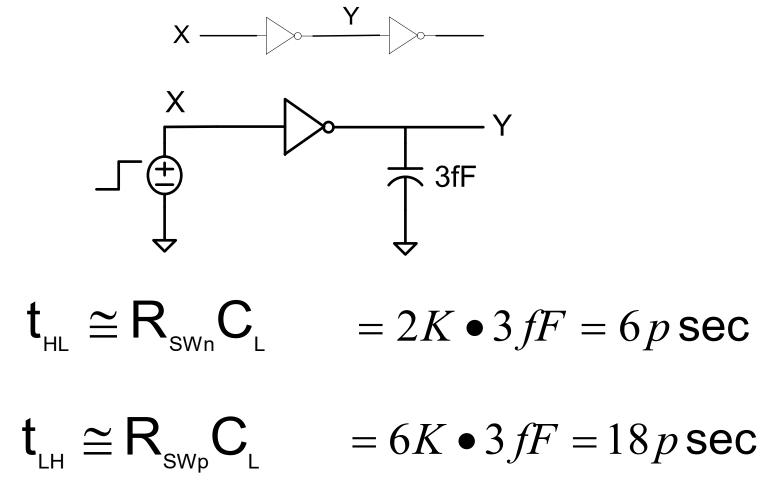

What are t<sub>HL</sub> and t<sub>LH</sub>?

Example: What is the delay of a minimum-sized inverter driving another identical device?

Loading effects same whether  $C_{GSp}$  and/or  $C_{GSn}$  connected to  $V_{DD}$  or GND

# Is a capacitor of 1.5fF small enough to be neglected?

## Area allocations shown to relative scale:

This example will provide insight into the answer of the question Example: What is the delay of a minimum-sized inverter driving another identical device? Assume  $V_{DD}$ =5V

Generalizing the Previous Analysis to Arbitrary Load

$t_{HL} \cong R_{SWn}C_{L}$  $t_{LH} \cong R_{SWp}C_{L}$  Example: What is the delay of a minimum-sized inverter driving another identical device?

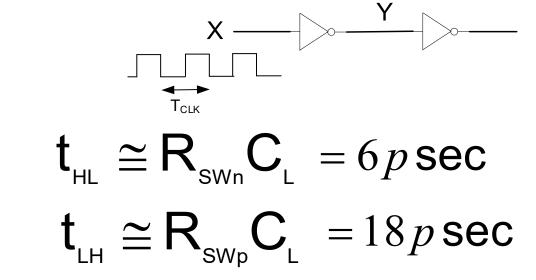

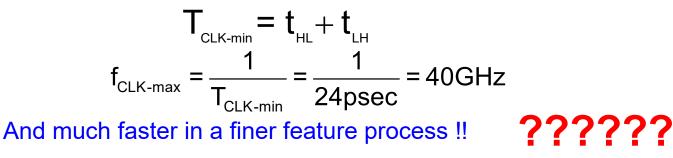

What would be the maximum clock rate for acceptable operation?

Example: What is the delay of a minimum-sized inverter driving another identical device?

What would be the maximum clock rate for acceptable operation?

What would be the implications of allowing for 10 levels of logic and 10 loads (FanOut=10)?

Example: What is the delay of a minimum-sized inverter driving another identical device? SUMMARY

This is very fast but even the small 1.5fF capacitors are not negligible ! These capacitors play a key role in determining the speed of a circuit ! Response time of logic gates

- Logic Circuits can operate very fast

- Extremely small parasitic capacitances play key role in speed of a circuit

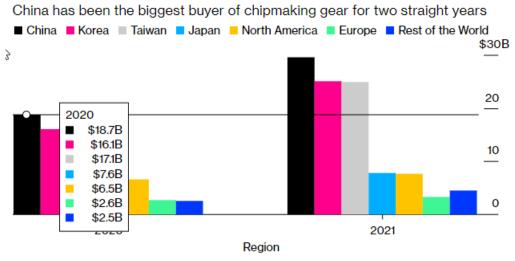

### **Some Observations about Technology and Politics**

Are the larger feature size technologies still used by industry today in the US or abroad?

GlobalData predicts that the <u>Chinese market will play a</u> <u>much smaller role for foreign suppliers by 2030</u>. More than 90% of the chips sold and used worldwide involve lowprocess production technology.

https://www.investmentmonitor.ai/analysis/china-lead-global-semiconductor-growth 2030#:~:text=Global %20semiconductor%20industry%20revolves%20around,Samsung 20Electronics%20and%20SK%20Hynix.

Source: SEMI

## **Some Observations about Technology and Politics**

Sept 2022

https://technode.com/2021/03/04/where-china-is-investing-in-semiconductors-in-charts/

China is the world's largest consumer of semiconductors, and the lion's share of revenue from purchasing these chips go to foreign firms. China consumed \$143.4 billion worth of wafers in 2020, and just 5.9% of them were <u>produced</u> by companies headquartered in China.

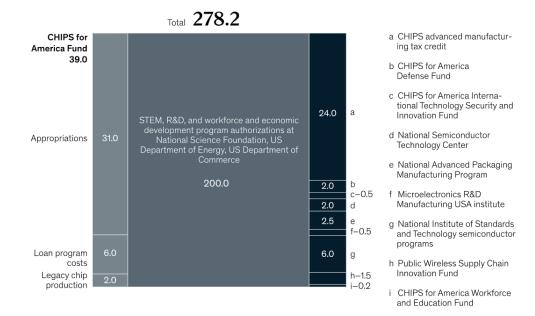

# The Chips Act of 2022

\$52 billion grant over five years to help grow the domestic semiconductor manufacturing. \$2 billion of which is to explicitly focus on legacy chip production. These chips are essential to the auto industry, the military, and other industries critical to our national security interests. The CHIPS and Science Act: Here's what's in it

#### ≪ 🗇 ⊥ □ Share Print Download Save

F

**By the numbers:** The CHIPS Act directs \$280 billion in spending over the next ten years. The majority—\$200 billion—is for scientific R&D and commercialization. Some \$52.7 billion is for semiconductor manufacturing, R&D, and workforce development, with another \$24 billion worth of tax credits for chip production. There is \$3 billion slated for programs aimed at leading-edge technology and wireless supply chains.

#### The CHIPS and Science Act of 2022 directs \$280 billion in spending over the next ten years, with the bulk for scientific R&D.

CHIPS and Science Act funding for 2022-26, \$ billion

Source: Creating Helpful Incentives to Produce Semiconductors (CHIPS) and Science Act of 2022, H.R. 4346, 117th Cong. (2022)

## How do I get CHIPS Act Funding?

<u>Breaking News</u>: The application for wafer manufacturers and suppliers of materials and equipment (e.g., chemicals and tools) was just released. Read the details <u>here</u>.

\$53 billion is available for semiconductor manufacturing and R&D, plus a 25% refundable tax credit for qualified CapEx. See below to discover where your business fits in

Need help? Book an appointment with our professional grant writing team <u>here</u> or email us: equity@chipsact.com

# **Stay Safe and Stay Healthy !**

# **End of Lecture 7**